核心工艺特点

镀层材质以铜、镍、金、锡为主,适配不同电子场景需求。

对镀层均匀性、厚度精度要求,通常需控制在微米级。

需结合载板材质(如陶瓷、树脂、硅)定制前处理和电镀参数。

核心工艺要求

镀层精度:厚度公差需控制在 ±0.1μm 内,镀层均匀性误差不超过 5%。

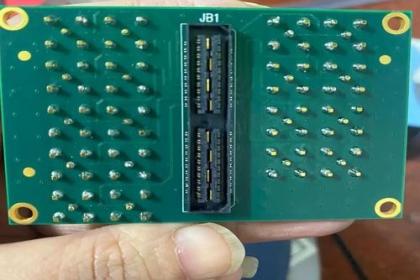

适配细线路需求:针对 IC 载板的微线路(线宽 / 线距<20μm),需避免镀层桥连、空洞。

材质兼容性强:需匹配 ABF 膜、BT 树脂、陶瓷等不同载板基材,不损伤基材性能。

主流镀层类型及用途

铜镀层:核心导电层,用于线路互联,厚度通常 1-5μm,要求高导电性和附着力。

镍镀层:中间阻挡层,防止铜扩散,厚度 0.5-2μm,提升后续镀层结合力。

金镀层:表面焊接 / 键合层,用于芯片键合或引脚焊接,厚度 0.1-1μm,分硬金(耐磨)、软金(易键合)。

锡镀层:低成本焊接层,替代部分金镀层,厚度 1-3μm,要求无针孔、可焊性好。

关键成本与质量控制点

成本核心:金盐、铜盐等贵金属原料占比高(约占原材料成本的 30%-40%),细线路加工导致的良率损耗会显著推高单位成本。

质量控制:需检测镀层厚度(XRF 检测)、附着力(胶带测试)、耐腐蚀性(盐雾测试),以及线路完整性(AOI 检测)。